Motivation

- Commercial, closed-source IP is a major drag on innovation in all technology spaces. Open-source hardware has the potential to ignite multiple paths in the semiconductor industry: increasing diversity by driving costs down, lowering the barrier to entry, and opening the door for customization.

- The idea of SoCs is starting to be applied to HPC, building chips from IP building blocks.

- New companies are being founded based on open source.

Goal

Using pre-verified open source IP, we want to create an open source silicon chip complete with a full software toolchain, including specialized instructions.

IP

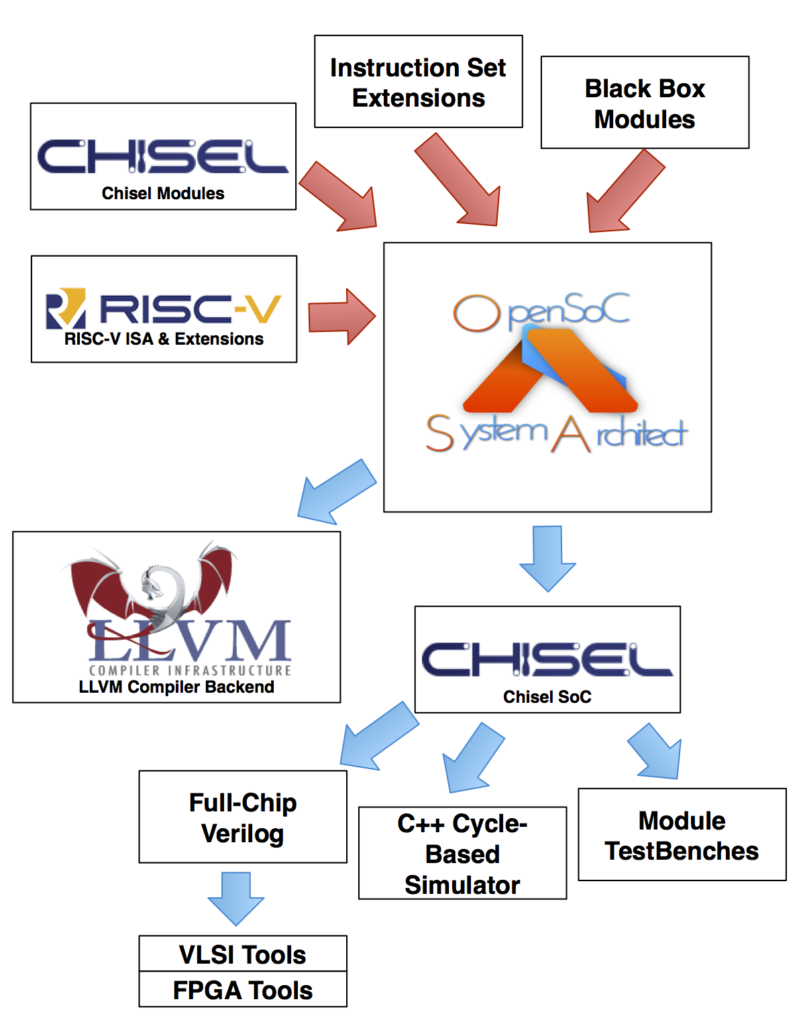

OpenSoC System Architect is made of and made possible by many different components.

Chisel (Constructing Hardware In a Scala Embedded Language) is an open-source hardware construction language developed at UC Berkeley that supports advanced hardware design using highly parameterized generators and layered domain-specific hardware languages.

- Hardware construction language (not C to Gates)

- Embedded in the Scala programming language

- Algebraic construction and wiring

- Abstract data types and interfaces

- Bulk connections

- Hierarchical + object oriented + functional construction

- Highly parameterizable using metaprogramming in Scala

- Supports layering of domain specific languages

- Sizeable standard library including floating-point units

- Multiple clock domains

- Generates low-level Verilog designed to pass on to standard ASIC or FPGA tools

- Open source on github with modified BSD license

- Complete set of docs

- Growing community of adopters

RISC-V (pronounced “risk-five”) is a new instruction set architecture (ISA) that was originally designed to support computer architecture research and education and is now set to become a standard open architecture for industry implementations under the governance of the RISC-V Foundation. The RISC-V ISA was originally developed in the Computer Science Division of the EECS Department at the University of California, Berkeley.

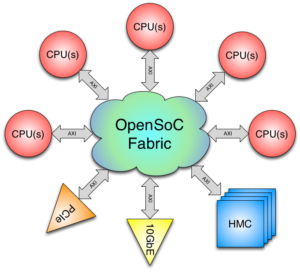

OpenSoC Fabric

LLVM

CoreGen

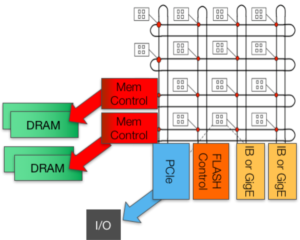

CoreGen is an integrated infrastructure that utilizes traditional compiler techniques to build and verify complex SoC designs. It’s essentially a compiler IR for SoC design and verification. CoreGen utilizes an intermediate representation that permits us to:

- Build high-level optimizations and verification of SoC control and data paths

- Build high-level descriptions of complex SoC’s

- Automatically build HDL representations of the SoC

- Automatically build LLVM compiler backend implementations of the SoC and any extensions

- Permits users to quickly and easily extend the SoC using new or existing IP

The result is significant reduction in design, implementation, and verification of complex SoC’s.

Tool Chain & Flow

OpenSoC System Architect takes these IP blocks and the users input design specs and extensions via the frontend to generate the CoreGen IR. OpenSoC Fabric "glues" all of the all intermediate modules together with a scalable NoC. CoreGen ensures the design correctness and continuity.